### **System-Level Testing of Embedded Analogue Cores in SoC**

Liquan Fang

2003

Ph.D. thesis University of Twente

Also available in print: <a href="http://www.tup.utwente.nl/catalogue/book/index.jsp?isbn=9036519195">http://www.tup.utwente.nl/catalogue/book/index.jsp?isbn=9036519195</a>

System-Level Testing of Embedded Analogue Cores in SoC

#### Promotiecommissie

Voorzitter:Prof.dr.ir. A. J. MouthaanUniv. Twente / EWIPromotor:Prof.dr.ir. T. KrolUniv. Twente / EWIAssistent-promotor:Dr.ir. H. G. KerkhoffUniv. Twente / EWILeden:Prof.dr.ir H. WallingaUniv. Twente / EWIProf.ir. A.J.M. van TuijlUniv. Twente / EWI

Prof.dr. G. Gielen KU Leuven

Prof.dr. J. Figueras Univ. Catalunya

The research described in this thesis was partially funded by the Dutch Technology Foundation (STW). The research was carried out at Testable Design & Testing of Microsystems research group (TDT), MESA+ research institute, University of Twente.

#### Twente University Press

Publisher:

Twente University Press, P.O. Box 217, 7500 AE Enschede, the Netherlands, www.tup.utwente.nl

Print: Océ Facility Services, Enschede

© Liquan Fang, Enschede, 2003

No part of this work may be reproduced by print, photocopy or any other means without the permission in writing from the publisher.

ISBN 9036519195

# SYSTEM-LEVEL TESTING OF EMBEDDED ANALOGUE CORES IN SOC

#### **PROEFSCHRIFT**

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof.dr. F.A. van Vught,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op donderdag 12 juni 2003 te 13.15 uur

door

Liquan Fang geboren op 23 januari 1973 te Xiaoshan, Zhejiang, China Dit proefschrift is goedgekeurd door de promotor Prof.dr.ir. T. Krol en de assistent-promotor Dr.ir. H. G. Kerkhoff

To Zhichun, Daniel and my parents

## Contents

| Acknowledgement                                                         | v   |

|-------------------------------------------------------------------------|-----|

| Summary                                                                 | vii |

| Abbreviations                                                           | ix  |

| Chapter 1. Introduction                                                 | 1   |

| 1.1 The role of IC testing                                              | 2   |

| 1.2 Digital testing and analogue testing                                |     |

| 1.2.1 Digital testing                                                   | 2   |

| 1.2.2 Analogue testing                                                  | 3   |

| 1.2.3 Mixed-signal testing                                              |     |

| 1.3 System-on-a-Chip (SoC) testing                                      |     |

| 1.4 Our approach for testing analogue embedded cores in SoC             | 6   |

| 1.5 Controllable input range and observable output range                | 9   |

| 1.6 Test-signal backtrace                                               |     |

| 1.7 Outline of the thesis                                               |     |

| 1.8 References                                                          | 12  |

| Chapter 2. Tolerance-box generation and propagation                     | 15  |

| 2.1 Introduction                                                        | 16  |

| 2.2 Core-based tolerance-box generation and propagation                 |     |

| 2.3 Sensitivity-analysis based tolerance-box generation and propagation |     |

| 2.3.1 Parameter-deviation model                                         | 19  |

| 2.3.2 Tolerance-box analysis for a stand-alone core                     | 22  |

| 2.3.3 Propagation algorithm                                             | 25  |

| 2.4 Example circuit and simulation results                              | 28  |

| 2.4.1 Example circuit                                                   |     |

| 2.4.2 Parameter-deviation model of the example circuit                  |     |

| 2.4.3 Simulation results                                                |     |

| 2.5 Conclusions                                                         | 35  |

| 2.6 References                                                          | 35  |

| Chapter 3. Test-signal backtrace                                                | 37       |

|---------------------------------------------------------------------------------|----------|

| 3.1 Introduction                                                                | 38       |

| 3.2 PID feedback-loop based test-signal backtrace approach                      |          |

| 3.2.1 General structure                                                         |          |

| 3.2.2 Theoretical background                                                    | 41       |

| 3.2.3 Steady-state error                                                        |          |

| 3.2.4 Sensitivity to a disturbance signal                                       |          |

| 3.2.5 Parameter tuning                                                          | 45       |

| 3.3 Time and frequency domain simulation with the LPF                           | 47       |

| 3.3.1 Example circuit and parameter tuning                                      | 47       |

| 3.3.2 Signal backtrace in the time and frequency domain                         |          |

| 3.4 Test-signal backtracing                                                     |          |

| 3.4.1 Structure of the test path                                                |          |

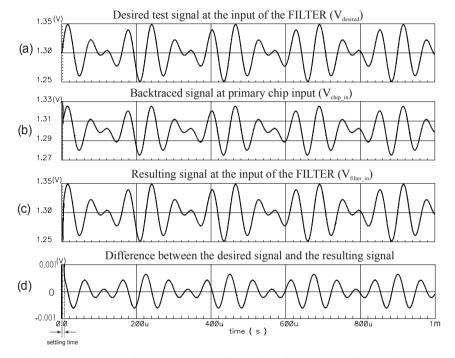

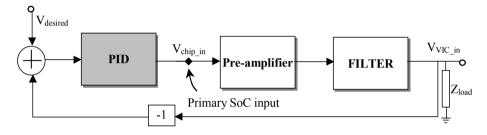

| 3.4.2 Test-signal backtracing for the test signals of the FILTER                |          |

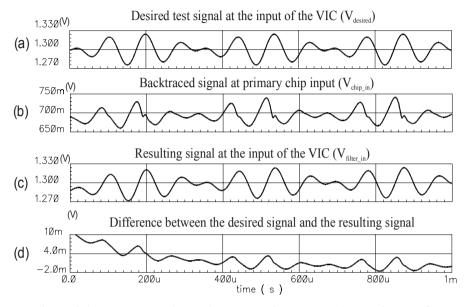

| 3.4.3 Test-signal backtracing for the test signals of the VIC                   |          |

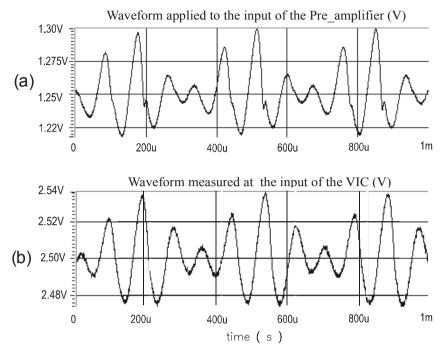

| 3.4.4 Experimental results                                                      |          |

| 3.5 Conclusions                                                                 |          |

| 3.6 References                                                                  | 57       |

| Chapter 4. Mixed-level modelling for analogue fault simulation                  | 59       |

| 4.1 Introduction                                                                | 60       |

| 4.2 Defect Oriented Test (DOT)                                                  | 61       |

| 4.3 Mixed-level modelling for analogue fault simulation                         |          |

| 4.4 Example circuit and the mixed-level model construction                      | 66       |

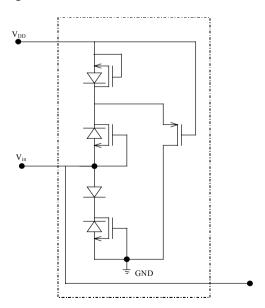

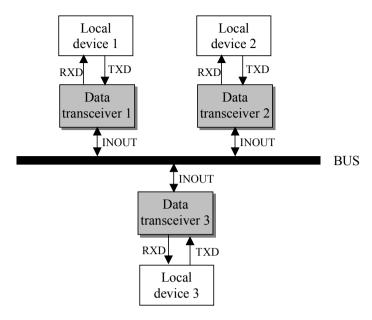

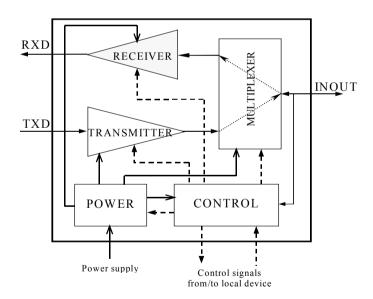

| 4.4.1 An actual industrial design: the data transceiver                         | 66       |

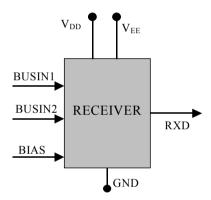

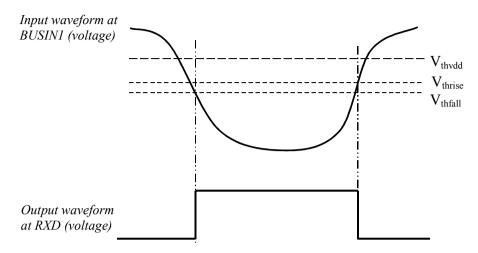

| 4.4.2 The function description of the RECEIVER block                            |          |

| 4.4.3 The mixed-level model of the RECEIVER block                               |          |

| 4.4.4 Verification of the functional behaviour of the mixed-level model         |          |

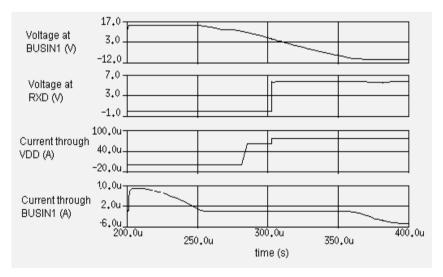

| 4.5 Fault-simulation results                                                    |          |

| 4.6 Conclusions                                                                 |          |

| 4.5 References                                                                  | 76       |

| Chapter 5. Mixed-signal P1500-compatible core-based testing architecture.       | 79       |

| 5.1 Introduction                                                                | 80       |

| 5.2 Core-based testing                                                          |          |

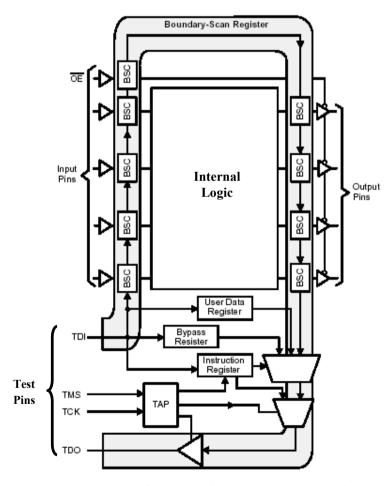

| 5.2.1 Digital boundary-scan standard IEEE 1149.1                                | 81       |

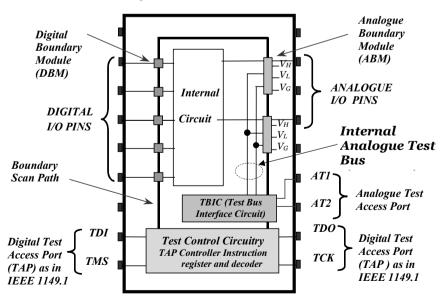

| 5.2.2 Mixed-signal test bus standard IEEE 1149.4                                |          |

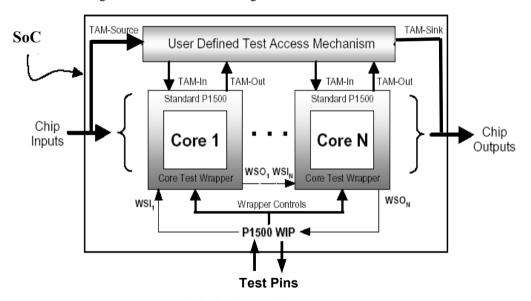

| 5.2.3 Digital core-based testing using the proposed standard IEEE P1500         |          |

| 5.2.4 The proposed mixed-signal core-based testing architecture                 |          |

| 5.3 The hardware implementation of the proposed core-based testing architecture |          |

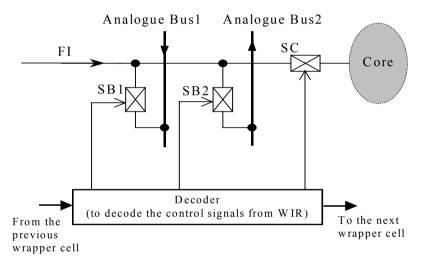

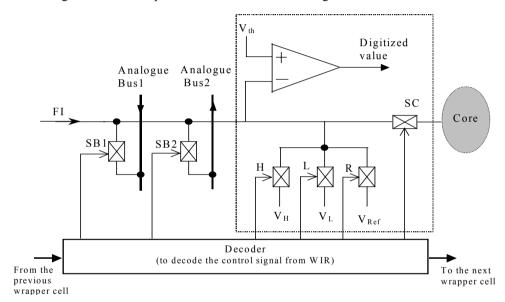

| 5.3.1 Analogue input wrapper cell                                               |          |

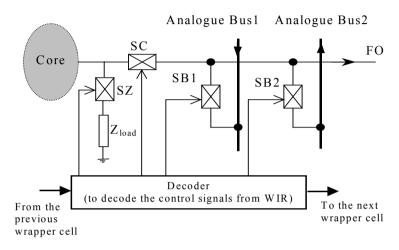

| 5.3.2 Analogue output wrapper cell                                              |          |

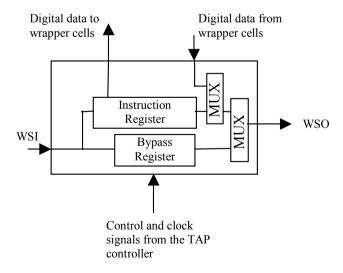

| 5.3.3 Wrapper instruction register                                              |          |

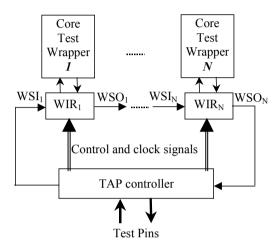

| 5.3.4 TAP controller                                                            |          |

| 5.3.4 User defined test access mechanism                                        |          |

| 5.4 Example circuit and simulation results                                      | 91<br>92 |

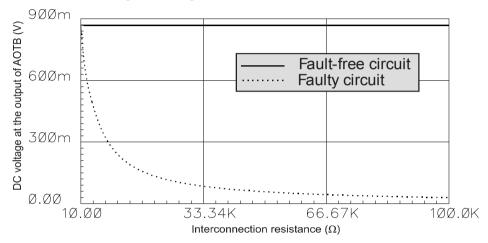

| 5.4.3Simulation results for the embedded core testing case.995.4.4Simulation results for the interconnection testing case.105.4.5Silicon area overhead of the proposed architecture.105.5Conclusions.105.6References.10Chapter 6.Conclusions and recommendations.106.1Conclusions.106.2Original contributions of this thesis.106.3Recommendations for future research.106.4Reference.10Appendix A.Parameter-deviation model and tolerance-box propagation algorithm.11A.1Parameter-deviation model.11A.2Tolerance-box propagation algorithm.11Appendix B.DC convergence of the proposed test-signal backtrace approach.11 | 5.4.2  | Simulation results for normal operation                      | 93  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------|-----|

| 5.4.5 Silicon area overhead of the proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.4.3  |                                                              |     |

| 5.5 Conclusions 10: 5.6 References 10:  Chapter 6. Conclusions and recommendations 10: 6.1 Conclusions 10: 6.2 Original contributions of this thesis 10: 6.3 Recommendations for future research 10: 6.4 Reference 10:  Appendix A. Parameter-deviation model and tolerance-box propagation algorithm 11: A.1 Parameter-deviation model 11 A.2 Tolerance-box propagation algorithm 11:  Appendix B. DC convergence of the proposed test-signal backtrace approach 11:                                                                                                                                                     | 5.4.4  | Simulation results for the interconnection testing case      | 101 |

| 5.5 Conclusions 10: 5.6 References 10:  Chapter 6. Conclusions and recommendations 10: 6.1 Conclusions 10: 6.2 Original contributions of this thesis 10: 6.3 Recommendations for future research 10: 6.4 Reference 10:  Appendix A. Parameter-deviation model and tolerance-box propagation algorithm 11: A.1 Parameter-deviation model 11 A.2 Tolerance-box propagation algorithm 11:  Appendix B. DC convergence of the proposed test-signal backtrace approach 11:                                                                                                                                                     | 5.4.5  |                                                              |     |

| Chapter 6. Conclusions and recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.5 Cc |                                                              |     |

| 6.1 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.6 Re | eferences                                                    | 103 |

| 6.1 Conclusions 106 6.2 Original contributions of this thesis 106 6.3 Recommendations for future research 106 6.4 Reference 106  Appendix A. Parameter-deviation model and tolerance-box propagation algorithm 116 A.1 Parameter-deviation model 117 A.2 Tolerance-box propagation algorithm 117  Appendix B. DC convergence of the proposed test-signal backtrace approach 117  List of publications 126                                                                                                                                                                                                                 | Chapt  | ter 6. Conclusions and recommendations                       | 105 |

| 6.2 Original contributions of this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.1 Cc | onclusions                                                   | 106 |

| 6.3 Recommendations for future research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                              |     |

| Appendix A. Parameter-deviation model and tolerance-box propagation algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                                                              |     |

| A.1 Parameter-deviation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6.4 Re | eference                                                     | 109 |

| A.1 Parameter-deviation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                                                              |     |

| A.2 Tolerance-box propagation algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | algori | thm                                                          | 111 |

| A.2 Tolerance-box propagation algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A.1 Pa | rameter-deviation model                                      | 111 |

| approach11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                              |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Appe   | ndix B. DC convergence of the proposed test-signal backtrace | 44- |

| List of publications12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | appro  | eacn                                                         | 117 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | List o | f publications                                               | 123 |

## Acknowledgement

Upon the completion of this thesis, I would like to thank all the people who have contributed to this thesis in one way or other. Specially, I would like to thank:

- my assistant promotor, Dr. ir. Hans G. Kerkhoff, for his invaluable guidance, advice, encouragement and conscientious review of the manuscript of this thesis. His constant confidence in the face of research uncertainties and his persistent questioning of our methods have been and will always be inspiring to me.

- my promotor, Prof. dr. ir. Thijs Krol, for his continuous encouragement and support during the last two years of this research work.

- Prof. dr. ir. Hans Wallinga for giving me a lot of support on my research work and personal life.

- Guido Gronthoud of Philips Research and Yizi Xing of Philips Semiconductors for giving me the opportunity to have the practical training in Philips and helping me a lot in other ways.

- my officemates Milan Stancic and Nur Engin for the nice and interesting discussions in a wide spectrum including mixed-signal testing, cars, child-care, computers, food, politics, etc.: the good mood in the office was sometimes the best thing keeping me going.

- my other TDT AIO colleagues Arun Antony Joseph, Herman Vermaak, Octavian Petre, Frank te Beest and Vladimir Zivkovic for the enjoyable discussions and the wonderful time we had.

- Rob Tijink for designing some circuits for this research work and providing high quality support for the CAD tools.

- Marcel Weusthof for helping me carry out the measurements.

- students M. C. Huijgen and M. H. ten Berge for implementing the mixed-signal corebased test architecture in CMOS technology.

- Cor Bakker and Frederik Reenders for their high quality maintenance of the PC network and fast and friendly support with all PC problems.

- Egbert Holl and Han Speek, for the maintenance of the HP-network.

- the administrative staff of ICE, the secretaries Annemiek Janssen, Miranda Wijk, Marie-Christine Predery, Margie Rhemrev, and the financial administrators Sophie Kreulen and Joke Vollenbroek. Thanks for keeping things organized and the work atmosphere enjoyable.

- Jay Kolhatker for the nice and interesting discussions we had (in the wide spectrum including the high-tech stuff, computers, food, language etc.)

- Ronald Tangelder for having the resourceful and enjoyable discussions during my first two years in the Netherlands.

- all the other members of ICE, who not only created a pleasant work environment but also gave me a lots of support for my work during the last four years.

- my Chinese friends for the wonderful time we had together.

Last but not the least, I want to thank my wife Zhichun and my son Daniel. They encourage and support me in every possible way to accomplish this Ph.D thesis. My parents' continuous encouragement and support also contribute immensely to my past and my today.

## Summary

The increasing time-to-market (TTM) pressures have created the demand for rapid design of single complex chips based on reusing the design and test data. On the other hand, the availability of shrinking process technologies makes it possible to integrate a number of digital and analogue functional blocks into a single chip, mixed-signal System-on-a-Chip (SoC). Due to the complexity of a SoC and the limited test access (lack of controllability and observability) for embedded analogue cores in the pin-limited SoC, there are a lot of technical challenges in the testing of embedded analogue cores in SoC.

A hierarchical approach has been employed for testing of embedded analogue cores in our research. In this approach, the test signals for each standalone analogue core in the SoC are selected first. Next, some test translation schemes are employed to translate the corelevel test signals into system-level test signals. The research presented in this thesis deals with the system-level testing of embedded analogue cores in SoC, i.e. how to translate the core-level test patterns into system-level.

The main task of the test-translation procedure is to propagate (backward and forward) those core-level test-input signals and test-output responses of each stand-alone core to the primary SoC inputs and outputs. Meanwhile, the corresponding tolerance boxes, which are the result of the allowed process-parameter variations during manufacturing, are also propagated to the primary SoC outputs for setting the corresponding optimal test thresholds. These thresholds are used to determine whether the chip under test is good or faulty during final production testing.

Tolerance-box generation in SoC testing is a very CPU-time consuming procedure with the traditional Monte-Carlo approach. By using the sensitivity analysis technique, this thesis proposes a new fast core-based tolerance-box generation and propagation approach for the testing of embedded analogue cores. In this approach, sensitivity analysis for each stand-alone analogue core is carried out first. Then, by using the proposed propagation algorithm, the tolerance box for the complete test path can be obtained. As the original points in our approach, the concept of the sensitivity is extended to core sensitivity and a new model for different categories of parameter deviations is proposed. The application of this approach to an example circuit shows that the proposed approach is very effective for the tolerance-box generation in the testing of embedded analogue cores.

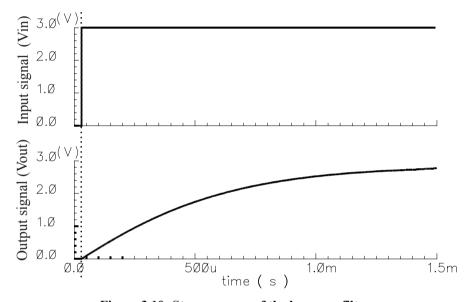

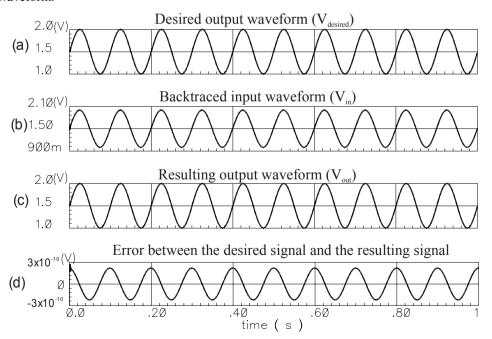

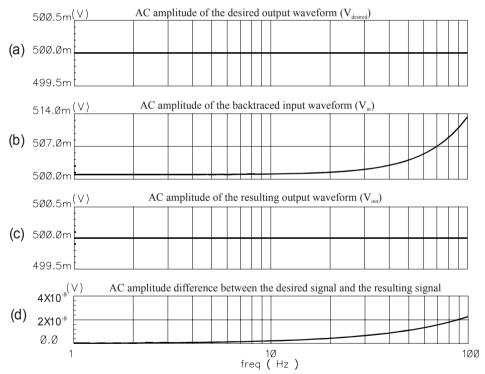

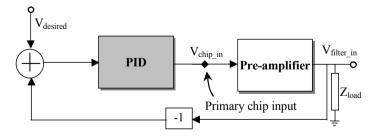

Test signal backtracing is the procedure to determine a stimulus at the primary SoC inputs that will produce the desired test signal at the inputs of the embedded cores under test. A PID (Proportional Integral Derivative) feedback loop based backtrace method has been proposed in our research. With this proposed method, the test input signal for the

embedded core could be backtraced to the primary SoC inputs in the time and frequency domain. Moreover, the computational effort for the backtrace procedure is low since it is quite easy to implement the PID controller in the high-level language during simulation. The presented theoretical analysis, simulation and measurement results show that the test-signals of the embedded cores can successfully be backtraced to the primary SoC inputs.

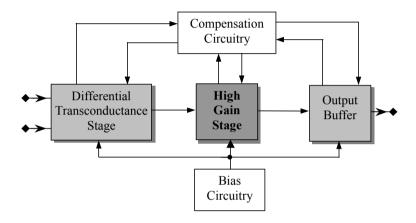

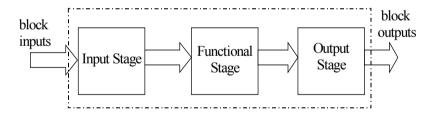

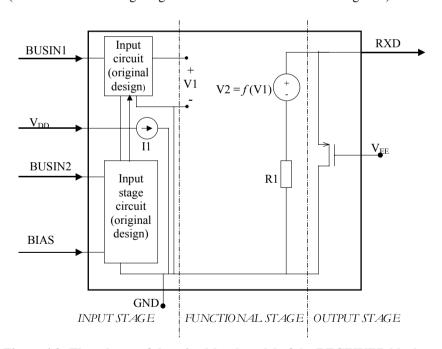

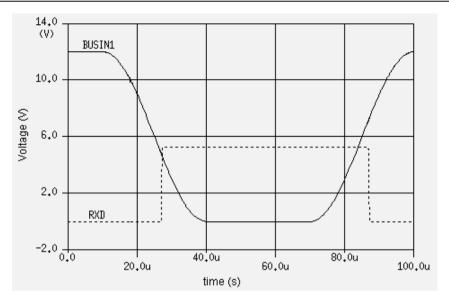

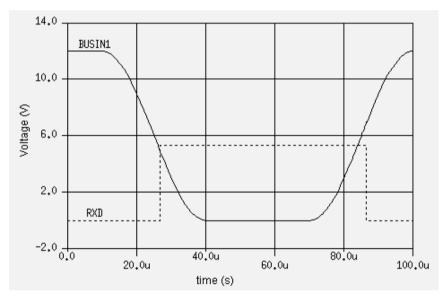

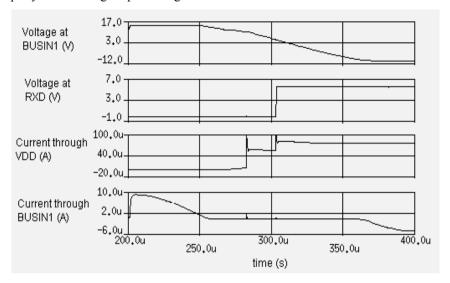

Analogue fault simulation is a CPU-time consuming procedure. A new general structure for mixed-level modelling with three stages is proposed in this thesis to speed up analogue fault simulation. In this structure, the original transistor-level circuits are reused for the input stage and output stage. The functional stage is an equation-based part to represent the function of the original fault-free block. This structure has been applied to one block of an actual industrial chip. The fault simulations have been carried out using this mixed-level model. The results show that this kind of mixed-level modelling can effectively reduce the fault-simulation time, while providing the same results for fault simulation.

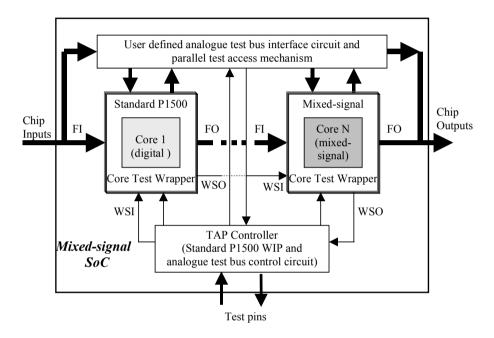

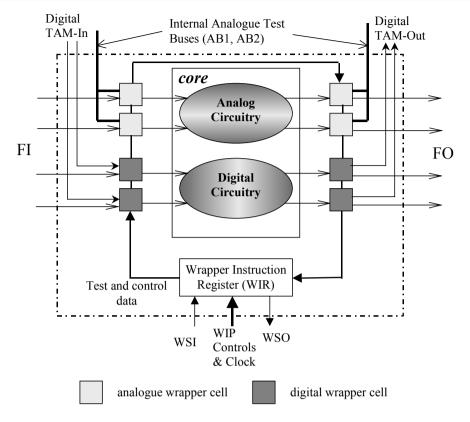

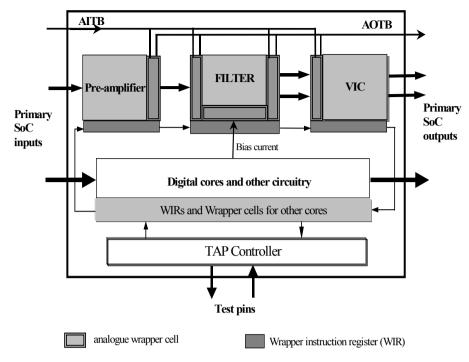

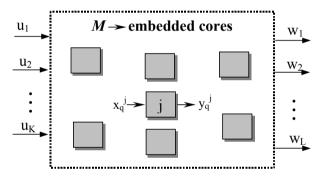

During test translation, some core-level test patterns might not be able to translate to the system-level due to the limited test access of the embedded cores. In order to solve this problem, a mixed-signal P1500-compatible core-based testing architecture is proposed in this thesis. The digital cores with the P1500 test wrapper can be directly used in this architecture to get extra test access because of its good compatibility. The new analogue input and output wrapper cells and analogue test buses have been designed and used to provide test access for the analogue testing of embedded mixed-signal cores. As an example, one analogue test path of a SoC including the new core-based architecture was evaluated by means of simulation. The simulation results show that the performance degradation and silicon area overhead of the extra DfT are acceptable for testing of embedded analogue cores.

Summarising, with the methods proposed in this thesis, the core-level test patterns for embedded analogue cores can be translated into the system-level test patterns. In other words, the research presented in this thesis provides an effective solution to the system-level testing of embedded analogue cores in SoC.

## **Abbreviations**

ADC Analogue to Digital Converter

ABM Analogue Boundary Module

AITB Analogue Input Test Bus

AOTB Analogue Output Test Bus

ATAP Analogue Test Access Port

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

AWG Automatic Test Pattern Generation

AWG Arbitrary Waveform Generator

BIST Build-In Self Test

BPF Band Pass Filter

BSC Boundary Scan Cell

DAC Digital to Analogue Converter

DfT Design for Test

DOT Defect Oriented Test

DSP Digital Signal Processing

ECUT Embedded Core Under Test

EDA Electronic Design Automation

FI Functional Input

FO Functional Output

IC Integrated Circuit

IP Intellectual Property

LPF Low Pass Filter

MNA Modified Node Analysis PCB Printed Circuit Board

PID Proportional Integral Derivative

PLL Phase Locked Loop

PPM Part Per Million

PWL Piece Wise Linear

RF Radio Frequency

SNR Signal-to-Noise Ratio

SoC System on a Chip

TAM Test Access Mechanism

TAP Test Access Mechanism

TAP Test Access Port

TBIC Test Bus Interface Circuit

TCK Test Clock

TDI Test Data Input

TDO Test Data Output

THD Total Harmonic Distortion

| TMS | Test Mode Selection |

|-----|---------------------|

| TTM | Time-To-Market      |

|     |                     |

VIC Voltage Current Converter

WCI Wrapper Control Interface

WIP Wrapper Interface Port

WIR Wrapper Instruction Registe

WIR Wrapper Instruction Register

WSI Wrapper Serial Input

WSO Wrapper Serial Output

## Chapter 1

## Introduction

This chapter starts with a short introduction into the area of IC (integrated circuits) testing. It is followed by a brief overview of digital, analogue and mixed-signal testing. Then, System-on-a-Chip (SoC) testing is introduced. Next, the main challenges in testing of embedded analogue cores in a SoC are discussed and later on our hierarchical approach is introduced. In this approach, the test patterns for the standalone cores are generated first, then these core-level test patterns are translated into system-level test patterns by using the methods proposed in this thesis. Finally, the outline of the thesis is given in the last section of this chapter.

#### 1.1 The role of IC testing

IC testing is a procedure to select a *faulty* chip or a *good* chip by applying the proper test stimuli generated by a test program to the chip under test, measuring the test responses and comparing these test responses with pre-defined thresholds. A *faulty* chip is here defined as the chip that has manufacturing defects and/or whose operations are out of the original design specifications.

The main reason for the necessity of production testing is the existence of unpredictable and uncontrollable phenomena in different steps of the manufacturing process. As the results of these imperfections in the manufacturing process, several types of defects can exist in manufactured ICs. The most common causes of defects in manufacturing are human errors, equipment failures, process instabilities, material instabilities, substrate inhomogeneity and lithographical spot defects [Sac98]. Those defects can cause various types of malfunctioning, depending on the IC topology and the nature of the defect.

On the other hand, nowadays consumers today demand high performance and quality in any of the electronic components that they buy [Rob97]. Low prices and years of problem-free operation with minimal maintenance are now the norm. In order for manufacturers to deliver such products, extensive testing procedures must be followed. This is to ensure that only good products are delivered to the consumers and that bad parts are rejected. A commonly mentioned rule of thumb of test is *the rule of ten* which suggests that the cost of detecting a bad component in a manufactured part increases tenfold at each level of assembly. Early discovering its presence of a defect chip is therefore most desirable. As a result, IC testing is very important for chip manufacturers.

In the semiconductor industry, the cost to fabricate a transistor has fallen dramatically, from one-tenth of a dollar cent in 1983 to less than one-thousandth of a cent today [Gar01]. At the same time, the cost of testing each transistor has remained relatively stable. As a result, it is expected that testing a transistor in the near future (around 2012) will cost the same amount of money as manufacturing it [Int01].

#### 1.2 Digital testing and analogue testing

#### 1.2.1 Digital testing

For conventional digital testing, the structural fault-model based testing approach and the standard stuck-at fault model have been widely used for a substantial period of time. The distinction between *good* and *faulty* is relatively clear for digital circuitry. As a result of that, CAD tools for automatic test-generation and test-circuitry insertion are already available for conventional digital testing since more than two decades. Since digital testing is not within the scope of this thesis, the details with regard to the digital testing are not discussed here. More information on the issue of digital testing, for instance delay fault testing and IDDQ testing, can be found in other literature e.g. the proceedings of International Test Conference.

#### 1.2.2 Analogue testing

An obvious difference between digital testing and analogue testing is that the test stimuli and/or the test responses are analogue signals in the latter [Mil98]. This difference makes analogue testing much more difficult than digital testing. As commonly known, the number of values in an analogue signal is infinite, though the range is limited. This means that the search space for potential test stimuli is infinite during the analogue test-pattern generation process.

To complicate matters even more, the specification of an analogue circuit allows some variations in the circuit characteristics because of the possible process-parameter variations during manufacturing. For instance, the nominal value for the gain of an amplifier is 10dB. But 9.99 dB is also acceptable. Therefore, these output ranges called tolerance-boxes should be determined during the test-development stage [Tia97]. During the final production testing, it has to be determined if the output is within a certain *range*, not if it has a specific value. This also increases the complexity of analogue testing.

In general, each analogue circuit has its own unique specification during design. It is therefore reasonable that a *good* chip can be selected during the final chip testing by checking whether the chip conforms to the original design specification. This test methodology is called specification-based testing. Specification-based tests offer the advantage of ensuring that a circuit that passes the test process will meet the requirements of the user. The test generation, however, is manual and derived from the specifications. Its disadvantage is that the implementation of the test program can be very expensive for certain circuits. For instance high-frequency measurements are required for RF circuit testing.

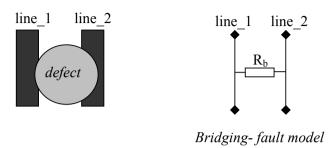

The alternative test development methodology is called structural fault-model based test. In this approach, the manufacturing defects are modelled by certain fault models (e.g. bridging fault model), which can be inserted into the circuit schematic to emulate potential faulty circuits. For those faulty circuits, circuit simulations are carried out with test signals as inputs and the outputs are compared to the output of the fault-free circuit. If the difference between a faulty circuit output and a fault-free circuit output exceeds a predefined threshold, then the fault can be detected by applying the corresponding test pattern. In this way, the test patterns for final production testing can be determined. The procedure of simulating the fault-free circuit and all the faulty circuits with all the potential test-input signals is called analogue fault simulation. The main advantages of the structural fault model-based test are that low-cost test patterns can potentially be generated, the performance of the test patterns can be evaluated with their fault coverage and it makes automatic test-pattern generation feasible.

One crucial issue in analogue structural testing is that the analogue fault simulation always requires extremely long simulation times. This is because the number of possible faults in the fault list is large and analogue circuit simulation at the transistor level is very time-consuming. A possible solution to reduce the fault-simulation time is to use high-level models for the faulty-free blocks in the fault simulation. This means that the fault-free blocks are simulated using high-level models in order to reduce the simulation time.

Meanwhile, the faulty block is simulated at transistor level for simple and accurate injection of the fault into the fault-free netlist [Kaa98]. Crucial for this method is the generation of suitable high-level models of the fault-free analogue functional blocks or cores.

Another important item for structural fault model-based testing is the generation of the tolerance box. During analogue fault simulation, the fault-free circuit and faulty circuit have different tolerance boxes. The tolerance boxes for the fault-free circuit and each faulty circuit have to be generated. Hence, the total number of tolerance-boxes is (n+1) if the number of faults in the fault list is n. Since normally the fault list is quite large in analogue fault simulation, it is very important to generate the tolerance boxes fast and efficiently [Fan02a].

#### 1.2.3 Mixed-signal testing

Besides the pure digital blocks and analogue blocks, it is quite often that there are mixed-signals blocks (e.g. ADC, DAC, PLL) in the mixed-signal ICs. During mixed-signal testing, some test stimuli and test responses are in the digital domain and others are in the analogue domain. More details with regard to ADC, DAC and PLL testing can be found in [Bus01].

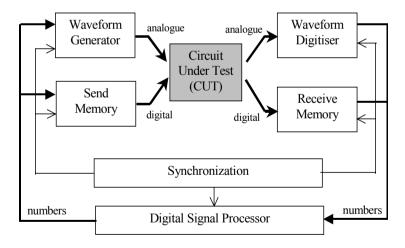

For mixed-signal testing, *DSP-based testing* is a very important approach [Rob96, Mah87]. The basic structure of a mixed-signal DSP-based test system is shown in Figure 1.1.

Figure 1.1: Fundamental structure of a DSP-based test system [Mah87].

In this structure, the *Synchronization* block provides the clock and phase synchronization for the whole system, analogue a well as digital parts, and the *Digital Signal Processor* block is the computing engine of the whole system. The basic idea behind DSP-based testing is that an analogue signal, for instance a sinus, is numerically computed by the digital computing engine and then applied to the *Waveform Generator* for conversion into the analogue domain. The resulting analogue signal is then applied to the *Circuit Under*

Test (CUT) from which its response is digitised by the Waveform Digitiser and passed on to the Digital Signal Processor for further processing. Depending on the measurement that is required, the appropriate software has to be loaded.

The procedure just described assumes that the *CUT* is an all-analogue chip. For the chip that produces digital output responses (e.g., ADC), the output digital signals are collected by a temporary RAM called the *Receive Memory* and then sent to the *Digital Signal Processor*. Similarly, if the *CUT* input is digital instead of analogue (e.g. DAC), the stimulus vectors would not be sent to the *Waveform Generator*, but to the *Send Memory* and replayed to the *CUT* input under the timing control of the *Synchronization* block (Figure 1.1).

In general, the DSP-based testing method offers a level of flexibility and repeatability that would be impossible with conventional analogue measurements. The analysis of captured data in the digital domain has also changed the measurement equipment capabilities substantially by the introduction of the concept of virtual instruments.

#### 1.3 System-on-a-Chip (SoC) testing

The increasing time-to-market (TTM) pressures have created the demand for rapid design of single complex chips based on reusing the design and test data. On the other hand, the availability of shrinking process technologies makes it possible to integrate a number of digital and analogue functional blocks into a single chip, mixed-signal System-on-a-Chip (SoC) [Dol02, Nag99, Oze00]. These functional blocks can be standard interface blocks (e.g. analog/digital converters, phase-locked loop), reusable IP (Intellectual Property) cores (e.g. memory or microprocessors), and custom-designed "user blocks". The SoC design concept makes the design process much more efficient than the conventional design methods and decreases the TTM because the system designer can order the cores from the core-providers, for instance on the internet [Dol02], on the Internet and reuse them in their SoC directly.

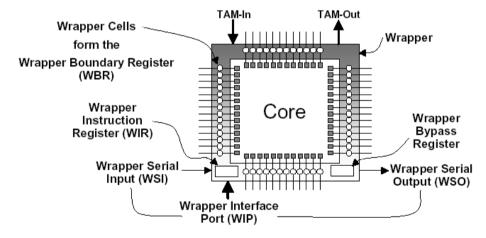

Digital core-based testing, which is being described by the proposed IEEE standard P1500 [P1500], is an effective test method for embedded digital cores in a SoC. In this approach, the test patterns for the stand-alone cores are generated by the core provider first. Afterwards, so-called test-wrapper cells as described in IEEE P1500 are used to provide test access for the embedded cores to apply the pre-generated test patterns [P1500].

Although the analogue circuitry part of mixed-signal SoCs comprises no more than 10-20% of the total circuitry of a chip, it takes up 70% of the test-development time [Nag99]. Besides test development, also in production, the analogue parts of a mixed-signal SoC can take a significant amount of time to test. In [Sma97] it was reported that analogue testing accounts for 50% of the production testing time. Besides the complexity of the SoC, another key factor that contributes to the SoC mixed-signal test complexity is the limited test access (lack of controllability and observability) for embedded analogue/mixed-signal cores in pin-limited SoCs. This hampers direct test-signal application and test-response evaluation. Therefore, how to develop effectively the efficient test patterns for testing the embedded analogue cores is a key issue in mixed-signal SoC testing.

Due to the complexity of testing the embedded analogue cores, a hierarchical approach is employed based on the previous concept of core-based testing. In the hierarchical approach, the test signals for each standalone analogue core in the SoC are selected first. Next, some test translation schemes are employed to translate the core-level test signals into system-level test signals.

The main previous work on system-level testing of embedded analogue/mixed-signals cores in SoC is presented in [Oze00, Oze01]. In this approach, by using the high-level models of the preceding cores and succeeding cores, the test signals at the inputs of the embedded core under test (ECUT) can be propagated to the primary SoC inputs and the test responses at the outputs of the ECUT can be propagated forwards to the primary SoC outputs. Therefore, high-level models of the embedded cores should be available if one wants to apply this test-translation scheme. In addition, the accuracy of the test signal/response propagation depends on the accuracy of the high-level models. Moreover, the tolerance-box propagation issue is not considered in the results of [Oze00] and [Oze01]. In our approach proposed in this thesis, however, high-level models of other cores are not required for the test translation and the tolerance-boxes are also propagated to the primary SoC outputs for setting the corresponding test thresholds.

#### 1.4 Our approach for testing analogue embedded cores in SoC

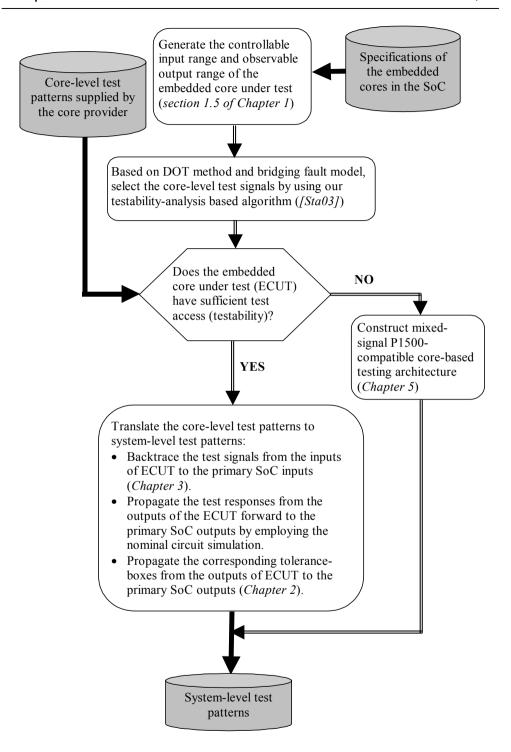

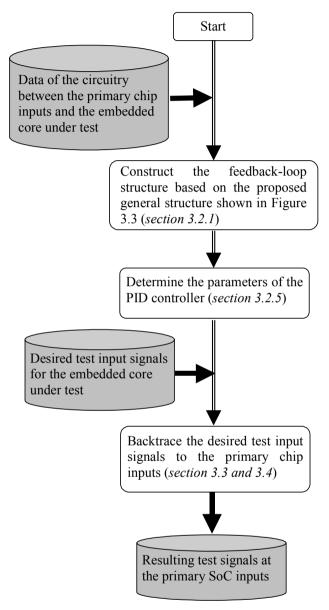

In our approach, the core-based testing concept is used for testing embedded analogue cores in SoC. The flow diagram of our proposed approach is shown in Figure 1.2. In this approach, the test signals for stand-alone cores are suggested by the test engineer or obtained from the core-provider first. Then, the core-level test patterns are translated into system-level ones because the test stimuli can only be applied at the primary SoC inputs and the test responses can only be observed at the primary SoC outputs during final production testing.

For the analogue cores whose test patterns are not supplied by the core-provider, e.g. locally designed cores, the test patterns have to be generated by the test engineer at the core-user side. In our approach, the controllable input range and observable output range of the embedded analogue cores is derived first, based on the topology of the SoC and the operation ranges of the preceding and succeeding cores. Then, our test-pattern generation method based on analogue testability analysis, DOT and the bridging-fault model [Sta03] is employed to select the core-level test multi-frequency AC signals. During the core-level test-pattern generation, the controllable input range and observable output range can narrow the search space for potential test patterns. Consequently, the fault-simulation time can be reduced. How to obtain the controllable input range and the observable output range of the analogue embedded cores is discussed in section 1.5.

Figure 1.2: The flow diagram of the proposed approach.

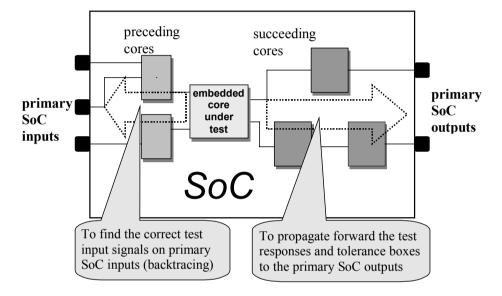

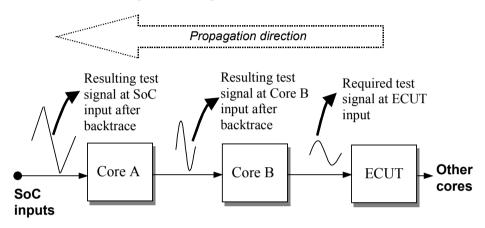

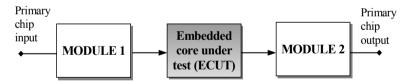

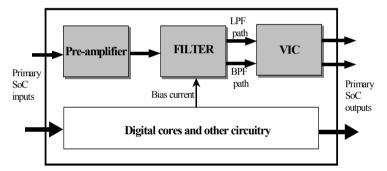

The main task of the test-translation procedure is to propagate (backwards and forwards) those core-level test-input signals and test-output responses of each stand-alone core to the primary SoC inputs and outputs as shown in Figure 1.3. Meanwhile, the corresponding tolerance boxes, which are the result of the allowed process-parameter variations during manufacturing, are also propagated to the primary SoC outputs for setting the corresponding test thresholds. These thresholds are set based on the tolerance-boxes of the faulty circuits and fault-free circuit. They are used to determine whether the chip under test is good or faulty during final production testing.

Figure 1.3: Illustration of translating the core-level test patterns to system-level ones.

More details about the test-signal backwards propagation (i.e. backtrace) is given in section 1.6. The test-response forward propagation can be carried out by employing normal circuit simulation. With regard to the tolerance-box generation and propagation, the traditional approach to obtain the tolerance-box is to perform Monte Carlo simulations at transistor level for the complete circuit. However, this becomes very CPU-time consuming for a SoC due to the complexity of a SoC. In our approach, a sensitivity-analysis based approach is proposed to reduce the CPU time used for the generation and propagation of the tolerance boxes [Fan02a].

During the test translation, it is also possible that some core-level test patterns cannot be realized for the embedded situation due to the limited test access. In order to test those embedded cores, extra controllable paths should be added to the SoC to allow access to inputs and outputs of each embedded core from the primary SoC pins. In our approach [Fan00], a new mixed-signal P1500-compatible core-based testing architecture is proposed to provide extra test access for the testing of low testability embedded cores.

#### 1.5 Controllable input range and observable output range

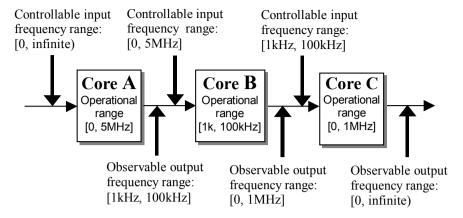

The controllable input range and observable output range of embedded analogue cores can be illustrated as following. Assume that there are three embedded analogue cores connected as depicted in Figure 1.4. The controllable input range for *Core B* is imposed by the operating range and behaviour of *Core A*. The controllable input range for *Core C* is determined by *Core A* and *Core B*. On the other hand, the whole output range is assumed to be observable for *Core C*. However, the observable output range of *Core B* is not the whole output range any more. It can be constrained by the operating range and behaviour of *Core C*. Similarly, the observable output range of *Core A* can be constrained by the operating range and behaviour of *Core B* and *Core C*.

Figure 1.4: Illustration of a test path with three embedded cores.

The controllable input range and the observable output range of embedded cores can be obtained by combining the operational range of the preceding and succeeding cores. The following discussion shows how to obtain the controllable input range and the observable output range. Without the loss of any generality, the operational frequency ranges of three embedded cores shown in Figure 1.4 are assumed to be [0,5MHz], [1kHz,100kHz] and [0,1MHz] respectively (see Table 1.1).

| Core   | AC operational range      |

|--------|---------------------------|

| Core A | Frequency: [0, 5MHz]      |

| Core B | Frequency: [1kHz, 100kHz] |

| Core C | Frequency: [0, 1MHz]      |

Table 1.1: The operational frequency range (-3dB point) of three cores.

With the data listed in Table 1.1, the controllable input frequency range and the observable output frequency range can be calculated as shown in Figure 1.5 by combining the corresponding operation frequency ranges of the preceding cores and the succeeding cores. Note that both the controllable input frequency range of *Core A* and the observable output frequency range of *Core C* are assumed to be [0, infinite). During the calculation, the controllable input frequency range of *Core B* can be obtained to be [0, 5MHz] by combining the range [0, infinite) and [0, 5MHz]. The controllable input frequency range of *Core C* can be calculated to be [1kHz, 100kHz] by combining [0, infinite), [0, 5MHz] and [1kHz, 100kHz]. Similarly, the observable output frequency range of *Core A* and *Core B* can be obtained to be [1kHz, 100kHz] and [0, 1MHz] respectively.

Figure 1.5: Illustration of the generation of the resulting controllable input ranges and the observable output ranges of the cores.

The operational frequency ranges of the embedded cores are assumed to be available during the above calculation. Actually, these operation ranges are available together with other specifications if the core is supplied by the core-provider. For instance, the analogue core HiAOP16 (High-Fi performance Audio-amplifier for driving speakers/headphones) is provided by the company Dolphin Integration [Dol02] with the following specifications available to the core user. The operational frequency range of this core is clearly specified to be from 100Hz to 24kHz in this table.

| Item                        | Specification                        |

|-----------------------------|--------------------------------------|

| Output load                 | 16 Ohm series to analog ground (VMC) |

| Output signal               | single-ended                         |

| Internal gain               | fixed by resistive feedback network  |

| Output voltage range        | 0.71 Vrms                            |

| SNR                         | 90 dB                                |

| Frequency band (-3dB point) | (100Hz, 24kHz)                       |

| THD                         | 70 dB with input frequency = 1 kHz   |

| Power consumption           | 2 400 μW with no load                |

| Technological process       | 0.35 μm TSMC / UMC                   |

| Single power supply         | 2.7 V to 3.6 V                       |

| Temperature range           | -40 °C to 85 °C                      |

Table 1.2: The specification of an analogue core (partly)

The controllable input range and observable output range of the analogue embedded cores are quite important for selecting the test signals for the standalone embedded cores. Due to the fact that the operation ranges of the embedded cores are provided as one part of the core specifications, the controllable input range and the observable output range can be

obtained by combining the operation ranges of the preceding and succeeding cores in the SoC as having been illustrated in the above-mentioned example.

#### 1.6 Test-signal backtrace

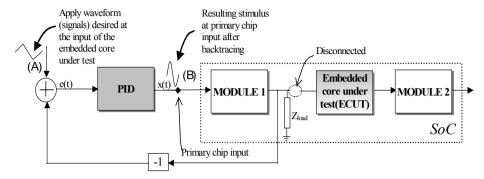

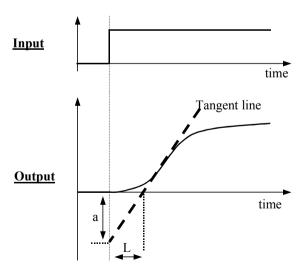

The test-signal backtrace procedure illustrated in Figure 1.6 can be defined as follows: given the DC, AC or transient signal desired at the input of the embedded core under test (ECUT), one requires to find the signal values or waveforms at the primary SoC inputs that result in the desired test signals at the inputs of ECUT.

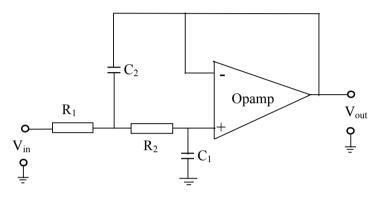

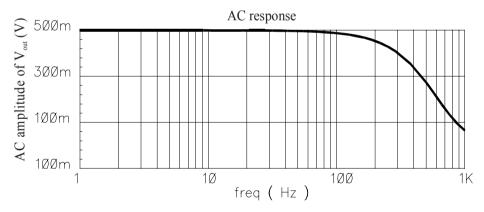

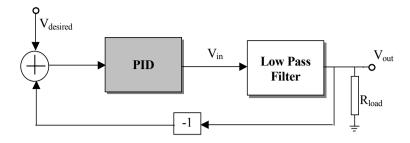

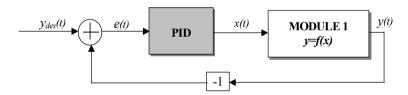

Figure 1.6: The illustration of the test-signal backtrace procedure.

In digital ATPG (automatic test-pattern generation), such a procedure finds an assignment of primary chip input values that cause a desired logic value to appear on a specified line in the circuit. While digital backtrace procedures are relatively easy to implement with the help of Boolean mathematics, there is no generic approach for backtracing analogue signals in mixed-signal SoC testing [Voo99]. The main reason is that the analogue test signal is continuous and the respective input-output relationships of the components used in analogue circuits are often expressed by nonlinear equations. In our approach [Fan02b], a new PID (Proportional Integral Derivative) [Ast95] feedback-loop based test-signal backtrace method is proposed.

#### 1.7 Outline of the thesis

This thesis is focussed on the system-level testing of analogue embedded cores in a mixed-signal SoC environment. The body of the thesis is organized as follows:

In *Chapter 2*, a fast tolerance-box generation method is proposed for the testing of analogue embedded cores. In this approach, the sensitivity analysis for each stand-alone analogue core is carried out first. Subsequently, the tolerance box for the entire analogue test path can be obtained by using our proposed propagation algorithm. The key features of this approach are: the introduction of the concept of core sensitivity and the development of a new model for different categories of parameter deviations to solve the problem that

parameter deviations for different cores can be possibly correlated. The theoretical analysis of this approach and the application to an example circuit are also presented and further mathematical details can be found in *Appendix A*.

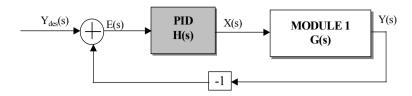

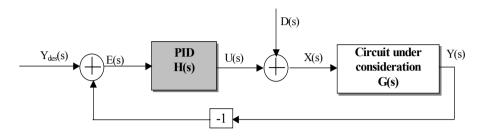

A promising solution to the test-signal backtracing problem is presented in *Chapter 3*. It is referred to as the PID feedback-loop based test-signal backtrace approach. Motivated by concepts in control theory, a feedback loop with PID controller is constructed for test-signal backtracing in this approach. With this method, the test-input signals of an embedded analogue core under test can be easily propagated backwards to the primary SoC inputs. The computational effort of the proposed approach is also quite low. Its application to an example circuit and the simulation results as well as measurement results are also presented. The theoretical analysis of this approach is provided in *Appendix B*.

The technique of reducing the massive analogue fault-simulation time by using high-level modeling of fault-free cores is discussed in *Chapter 4*. The crucial issue for using this technique is the generation of the high-level models suitable for fault simulation. A new mixed-level model structure with three stages is proposed [Fan01]. In this structure, the original transistor-level circuits are reused for the input stage and output stage. The functional stage is an equation-based part to represent the function of the original fault-free block. This structure can guarantee the proper operation of the complete model if preceded or succeeded by a faulty block/core. This approach has been applied to an actual industrial chip and the fault simulations with the mixed-level model have been carried out.

Chapter 5 proposes a new mixed-signal P1500-compatible core-based testing architecture to provide extra test access for embedded cores that have low testability. In this architecture, the ideas developed in IEEE P1500 [P1500] are extended for embedded analog/mixed-signal cores. By using a wrapper-cell structure and analogue test buses, the digital/analogue test stimuli can be transported from the external SoC inputs to the inputs of the ECUT, and subsequently the digital/analogue test responses can be propagated from the ECUT to the external SoC outputs. In this architecture, the digital input and output wrapper cells can be identical to the ones suggested within P1500. New analogue input/output wrapper cells and an enhanced TAP (Test Access Port) controller have been developed. The proposed new core-based testing architecture has been applied to a locally designed SoC and the simulation results together with the overhead calculation are presented in this chapter.

Chapter 6 summarizes the research results and highlights our original contributions. Recommendations for further research work in the field of testing of embedded analogue cores in mixed-signal SoC are also given in this chapter.

#### 1.8 References

- [Ast95] K. Astrom and T. Hagglund, "PID controllers: theory, design and tuning," Instrument of Society America, ISBN:1-55617-516-7, USA, 1995.

- [Bus01] M. L. Bushnell and V. D. Agrawal, "Essentials of electronic testing for digital, memory & mixed-signal VLSI circuits," Kluwer Academic Publishers, ISBN: 0-7923-7991-8, 2001.

- [Dol02] Dolphin Integration, "Jazz Line of analog and mixed-signal virtual components," http://www.dolphin.fr/flip/analog/analog overview.html

- [Fan00] L. Fang, M. Stancic and H. G. Kerkhoff, "Mixed-signal core-based testing," *Inf. Proc. of European Test Workshop (ETW) 2000*, pp. 279-280, May 2000.

- [Fan01] L. Fang, G. Gronthoud and H. G. Kerkhoff, "Reducing analogue fault-simulation time by using high-level modeling in Dotss for an industrial design", *Proc. of IEEE European Test Workshop*, ISBN 0-7695-1877, Stockholm, Sweden, pp. 61-67, 2001.

- [Fan02a] L. Fang and H. G. Kerkhoff, "Sensitivity analysis based tolerance-box generation and propagation in mixed-signal SoC testing", *Proc. of 7<sup>th</sup> IEEE European Test Workshop*, Corfu, Greece, pp. 255-260, May 2002.

- [Fan02b] L. Fang and H. G. Kerkhoff, "PID feedback based backtrace method for mixed-signal testing," *Proc. of 8th IEEE International Mixed-Signal Testing Workshop*, Switzerland, pp. 147-152, 2002.

- [Gar01] R. Garcia, "Distributed test strategy cuts cost," *Test & Measurement World (on line)*, November 2001.

- [Int01] "International technology roadmap for semiconductors, 2001 edition," <a href="http://public.itrs.net/Files/2001ITRS/Home.htm">http://public.itrs.net/Files/2001ITRS/Home.htm</a>

- [Kaa98] V. Kaal, "Structural test generation for analog macros", Ph.D. thesis, University of Twente, the Netherlands, 1998.

- [Mah87] M. Mahoney, "DSP-based testing of analogue and mixed-signal circuits," IEEE Computer Society Press, ISBN: 0-8186-0785-8, 1987.

- [Mil98] L. S. Milor, "A tutorial introduction to research on analog and mixed-signal circuit testing," *IEEE Trans. Circuits Systems—II: Analog and Digital Signal Processing*, vol. 45, no. 10, pp. 1389-1407, 1998.

- [Nag99] N. Nagi, "System-on-a-chip mixed-signal test: issues, current industry practices and future trends," *Proc. of 5th International Mixed Signal Testing Workshop*, Whistler, BC, Canada, pp. 201-211, 1999.

- [Oze00] S. Ozev, I. Bayraktaroglu and A. Orailoglu, "Test synthesis for mixed-signal SOC paths," *Proc. of Design, Automation and Test in Europe (DATE) Conference*, pp. 128-133, 2000.

- [Oze01] S. Ozev and A. Orailoglu, "System-level test synthesis for mixed-signal designs," *IEEE Trans. Circuits and Systems—II: Analog and Digital Signal Processing*, vol. 48, no. 6, pp. 588-599, June 2001.

- [P1500] Homepage of IEEE P1500 working group, <a href="http://grouper.ieee.org/groups/1500/">http://grouper.ieee.org/groups/1500/</a>.

- [Rob96] G. W. Roberts, "Metrics, techniques and recent developments in mixed-signal testing," Proc. of IEEE/ACM International Conference on Computer-Aided Design, pp. 514-521, Nov. 1996.

- [Rob97] G. W. Roberts, "Improving the testability of mixed-signal integrated circuits," *Proc. of IEEE Custom Integrated Circuits Conference*, pp. 214-221, May 1997.

- [Sac98] M. Sachdev, "Defect Oriented Testing for CMOS analog and digital circuits", Kluwer Academic Publishers, ISBN 0-7923-8083-5, 1998.

- [Sta03] M. Stancic, "Test selection for analogue cores based on the testability transfer function," Ph.D thesis, University of Twente, Enschede, the Netherlands, 2003.

- [Sma97] C. H. Small, "Mixed-signal methods shift gears for tomorrow's systems-on-a-chip," *Computer Design*, October 1997.

- [Tia97] M. W. Tian and C. J. R. Shi, "Rapid frequency domain analog fault simulation under parameter tolerances," *Proc. of Design Automation Conference (DAC97)*, pp. 275-280, 1997.

- [Voo99] R. Voorakaranam and A. Chatterjee, "Hierarchical test generation for analog circuits using incremental test development," *Proc. of IEEE VLSI Test Symposium* (VTS), pp. 296–301, April 1999.

## Chapter 2

## Tolerance-box generation and propagation

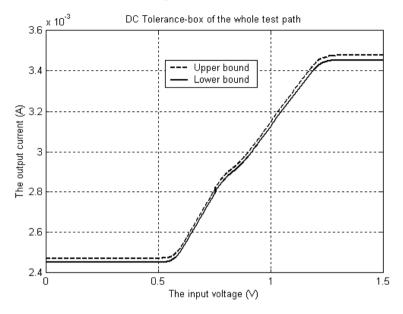

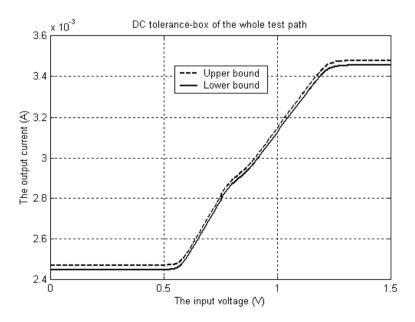

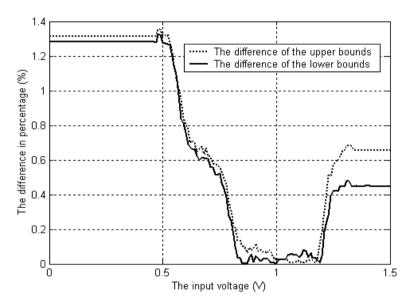

In this chapter, a sensitivity-analysis based approach is proposed to reduce the CPU time used for the tolerance-box generation and propagation in mixed-signal System-on-Chip (SoC) testing. The sensitivity analysis for each stand-alone analogue core is carried out first in this approach. Next the tolerance box for the entire analogue test path can be obtained by using the proposed propagation algorithm. Compared to the normal sensitivity analysis, the concept of core sensitivity is introduced for the proposed propagation algorithm. Moreover, in order to solve the problem that the parameter deviations for different cores can be possibly correlated, a new model for different categories of parameter deviations is also proposed. The presented simulation results show that this new approach is much faster (about 140 times) than the CPU-time consuming Monte Carlo simulation approach while the loss of accuracy is smaller than 1.36%.

#### 2.1 Introduction

As discussed in Chapter 1, the tolerance box is a fundamental issue for analogue testing because the specification of an analogue circuit allows for some variations in the circuit characteristics. These variations are a result of the allowed deviations of the process parameters. During analogue fault simulation, as a result, the responses for both good and faulty circuits will lie in bands. They are called good-response tolerance box and faulty-response tolerance box respectively [Tia97, Kaa98]. These tolerance-boxes are quite important for selecting the test signals and setting the optimal test thresholds. During test pattern generation, the test signal is selected if the overlap of the corresponding good-response and faulty-response tolerance-boxes is minimal. Meanwhile, the optimal test thresholds, which determine whether the chip under test is good or faulty during production testing, are set to minimize the detect error based on the tolerance-boxes.

Generally, the fault-free circuit and faulty circuit have different tolerance boxes. Therefore, for the fault-free circuit and each faulty circuit, the corresponding tolerance box should be generated. The total number of tolerance-boxes is therefore (n+1) if the number of faults in the fault list is n. Since normally the fault list is quite large in analogue fault simulation, it is very important to generate the tolerance box fast and efficiently.

The traditional and most widely used approach in the past to obtain the tolerance box is to perform Monte Carlo simulations at transistor level for the complete circuit. With this technique, the simulation is repeated for random combinations of values chosen from within the range of each parameter. Unfortunately, if the number of iterations for the simulation is not very large, the Monte Carlo simulation always underestimates the tolerance box [Shi99]. Therefore, this can be the source to produce non-robust test sets resulting that a fault undetectable at a given test point may be claimed to be detectable. Accurately determining the bounds on the circuit performance requires a large number of simulations. Therefore, this method becomes very CPU-time consuming if the chip becomes large.

In recent years, some methods have been proposed to speed up the tolerance-box generation in analogue fault simulation. The interval-analysis method has been used to calculate tolerance boxes for linear analogue circuits in [Tia96, Tia97, Tia00, Shi99]. In order to improve the efficiency and accuracy of interval-arithmetic based tolerance analysis, a genetic algorithm has been used for optimisation in [Fem99]. In [Ham93], sensitivity analysis is used to calculate the tolerance for analogue circuit testing.

However, because the number of transistors in mixed-signal SoC and the number of faults in the fault list are quite large, all the above-mentioned methods are not suitable for the tolerance-box generation in mixed-signal SoC testing. A solution to the fast tolerance-box generation and propagation in mixed-signal SoC testing is still not available.

As we know, the average simulation time of the SPICE-based circuit simulators for linear circuits is in the order of  $O(M^3)$  with M being the number of nodes. For nonlinear circuits it becomes even worse, and hence it is advantageous to break up a single set of nodes into a number of smaller sub-circuits [Vla94]. Moreover, with the increase of M, the advantage of breaking up the large circuit into small sub-circuits becomes more significant. On the other hand, due to the complexity of SoC, the chip is always partitioned into several

smaller functional cores [Nag99, Oze00], or called analogue virtual components in [Dol02]. Therefore, with respect to the tolerance-box generation in large mixed-signal SoC, the total simulation time can be reduced if the tolerance-box for the complete test path can be obtained by performing the simulations of each stand-alone (relatively small) analogue core and combining those tolerance boxes with a simple propagation algorithm.

Motivated by this idea, a novel fast sensitivity-analysis based tolerance-box generation and propagation algorithm for the analogue test paths in mixed-signal SoC consisting of analogue embedded cores is proposed in this chapter. In our approach, the sensitivity analysis is carried out for each stand-alone core first. Then, by using the proposed propagation algorithm, the tolerance box for the whole test paths with analogue embedded cores can be obtained.

#### 2.2 Core-based tolerance-box generation and propagation

In general, the core-based tolerance-box generation approach consists of the following two steps. In the first step, the tolerance box for each stand-alone analogue core in the test path is generated. In the second step, the tolerance-box for the whole analogue test path is obtained by using an algorithm to combine the tolerance boxes obtained in the first step. As discussed in the previous section, the total simulation time used for tolerance-box generation can be reduced because the simulation is carried out on relatively small cores, instead of the large whole SoC [Fan01a, Fan01b, Fan02].

However, during manufacturing the whole chip is facing the same process conditions, the parameter deviations of different cores are therefore correlated, which are mainly caused by the process deviations [Saa00]. Because of this correlation, the tolerance boxes for different cores in the same SoC are correlated. This correlation issue will be a big hamper in the propagation step of the core-based tolerance-box generation approach. Hence, in order to apply this core-based tolerance-box generation approach, the crucial problem with regard to the correlation of the parameter deviations for different cores should be solved.

Additionally, there are some other general requirements for applying the core-based tolerance-box generation approach. First of all, the computational effort for generating the tolerance-box for stand-alone cores should not be high. Second, the data format of the obtained tolerance box for a stand-alone core should be suitable for propagation. Third, the computational effort for propagation should be low.

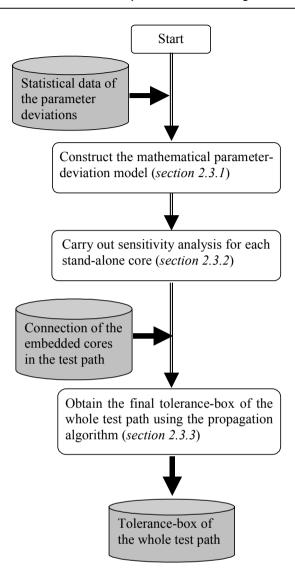

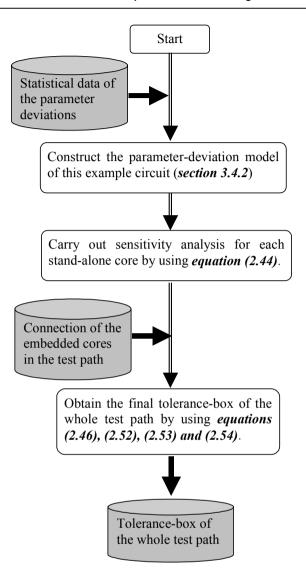

In order to respect the above-mentioned requirements, a sensitivity-analysis based tolerance-box generation and propagation method is proposed. The flow chart of this approach is shown in Figure 2.1. The sensitivity analysis is employed in this approach because it is already known that the sensitivity analysis can be used to estimate the worst-case response of any analogue circuit and this method is known to be not computationally expensive [Shi99, Ogr94]. Compared to the normal sensitivity analysis, two new items are proposed to make the sensitivity-analysis approach able to be used for core-based tolerance-box propagation. First, the concept of core sensitivity is proposed to enable the propagation. Second, a new model of different sorts of parameter deviations is proposed to solve the problem that the parameter deviations for different cores could be correlated.

Figure 2.1: The flow chart of the proposed tolerance-box generation and propagation approach.

The details of the items in the flow chart shown in Figure 2.1 are discussed in the next section. First, the mathematical model of the parameter deviations for different embedded analogue cores in SoC is proposed in subsection 2.3.1. Afterwards, the sensitivity-analysis based tolerance-box generation method for a stand-alone core is discussed in subsection 2.3.2. Finally, in subsection 2.3.3, the concept of core sensitivity is defined and the propagation algorithm is proposed.

## 2.3 Sensitivity-analysis based tolerance-box generation and propagation

In this section, the details of the proposed tolerance-box generation and propagation approach are discussed, including the parameter-deviation model, the tolerance-box analysis for a stand-alone core and the propagation algorithm.

#### 2.3.1 Parameter-deviation model

As indicated in section 2.2, the parameter deviations of different embedded cores in the same SoC could be correlated. As a result of that, the tolerance boxes of different cores could be correlated. This correlation issue is hampering the application of the propagation algorithm in the core-based tolerance-box generation approach. In order to solve this problem, a mathematical model of the parameter deviations for different embedded analogue cores in SoC is proposed in this subsection.

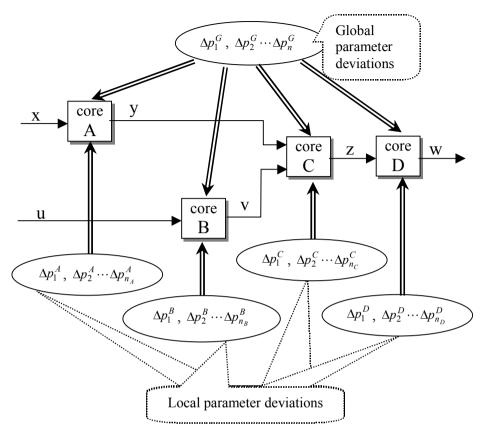

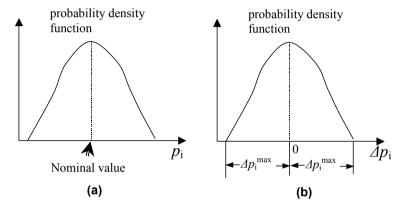

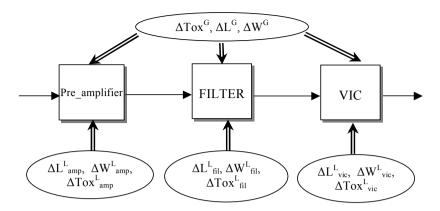

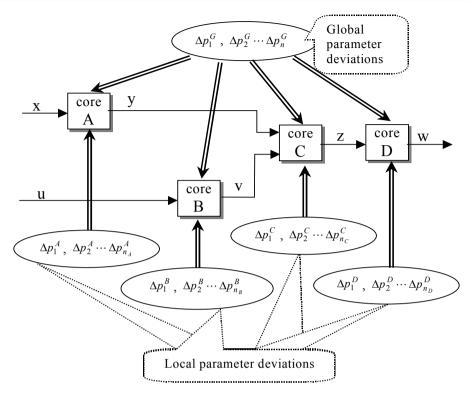

As an illustration without loss of any generality, core A, core B, core C and core D are connected as shown in Figure 2.2. In this figure, the new mathematical model for different categories of parameter deviations is also shown. In Figure 2.2,  $\Delta p_i^G (i=1,2,\cdots,n)$  are the deviations of the possible *global* parameters for all the cores (G). The deviations of the *local* parameters for core A, core B, core C and core D are  $\Delta p_i^A (i=1,2,\cdots,n_A)$ ,  $\Delta p_i^B (i=1,2,\cdots,n_B)$ ,  $\Delta p_i^C (i=1,2,\cdots,n_C)$  and  $\Delta p_i^D (i=1,2,\cdots,n_D)$  respectively. One point that should be made clearly here is that the global parameter deviations and local parameter deviations defined in this model have only a mathematical meaning. The real physical parameter deviations in each core are the combinations of local parameter deviations and global parameter deviations. For instance, the real parameter deviation in core B is a specific mathematical combination of  $\Delta p_i^G (i=1,2,\cdots,n)$  and  $\Delta p_i^B (i=1,2,\cdots,n_B)$ . Moreover, the deviations  $\Delta p_i^G (i=1,2,\cdots,n)$ ,  $\Delta p_i^A (i=1,2,\cdots,n_A)$ ,  $\Delta p_i^B (i=1,2,\cdots,n_B)$   $\Delta p_i^C (i=1,2,\cdots,n_C)$  and  $\Delta p_i^D (i=1,2,\cdots,n_D)$  are made to be mutually independent when the model is constructed. In other words, the local parameter deviations in different cores and the global parameter deviations in this model are independent from each other.

Although the local parameter deviations in different cores are mutually independent in this model, as proved in Appendix A, the correlation between the parameter deviations of different cores can be modelled using the same global parameter deviations.

Figure 2.2: Illustration of the generic system structure with different categories of parameter deviations.

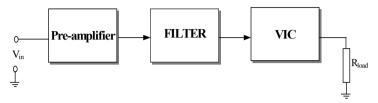

In order to show how to use the equations presented in Appendix A to construct the parameter-deviation model, a simple example is presented as following. Consider a test path containing three embedded analogue cores: the Pre\_amplifier, the FILTER and the VIC (Figure 2.6). The deviation of the *channel length* of the MOS transistors in these three embedded cores is the parameter deviation considered here. First of all, a parameter-deviation model is constructed for this example. In this model, the global parameter deviation is  $\Delta L^G$  and the local parameters deviations for the Pre\_amplifier, the FILTER and the VIC are  $\Delta L_{amp}^L$ ,  $\Delta L_{fil}^L$  and  $\Delta L_{vic}^L$  respectively. The real physical channel length deviation in these three cores are  $\Delta L_{amp}$ ,  $\Delta L_{fil}$  and  $\Delta L_{vic}$ . The mean value and variance of  $\Delta L_{amp}$ ,  $\Delta L_{fil}$  and  $\Delta L_{vic}$  are specified in the available statistical data as following:

$$\mu_{\Delta L_{amp}} = \mu_{\Delta L_{fil}} = \mu_{\Delta L_{vic}} = 0 \tag{2.1}$$

$$(\sigma_{\Delta L_{amp}})^2 = (\sigma_{\Delta L_{fil}})^2 = (\sigma_{\Delta L_{vic}})^2 = 2.79 \times 10^{-16}$$

(2.2)

Because these three cores are embedded in the same SoC, the transistor channel length deviations in these three cores are correlated. The correlation coefficients between them are given as:

$$\rho_{\Delta L_{amp},\Delta L_{fil}} = 0.93 \tag{2.3}$$

$$\rho_{\Delta L_{fil},\Delta L_{vic}} = 0.93 \tag{2.4}$$

$$\rho_{\Delta L_{amn},\Delta L_{vic}} = 0.9 \tag{2.5}$$

According to equation (A.1) in appendix A, the real physical channel length deviation in these three embedded cores can be expressed as:

$$\Delta L_{amp} = a_1 \cdot \Delta L^G + b_1 \cdot \Delta L_{amp}^L \tag{2.6}$$

$$\Delta L_{fil} = a_2 \cdot \Delta L^G + b_2 \cdot \Delta L_{fil}^L \tag{2.7}$$

$$\Delta L_{vic} = a_3 \cdot \Delta L^G + b_3 \cdot \Delta L_{vic}^L \tag{2.8}$$

Using equations (A.2), (2.6), (2.7) and (2.8), the mean value of the real length deviations in these three cores can be expressed as:

$$\mu_{\Delta L_{amp}} = a_1 \cdot \mu_{\Delta L^G} + b_1 \cdot \mu_{\Delta L_{amp}} \tag{2.9}$$

$$\mu_{\Delta L_{fil}} = a_2 \cdot \mu_{\Delta L^G} + b_2 \cdot \mu_{\Delta L_{fil}} \tag{2.10}$$

$$\mu_{\Delta L_{vic}} = a_3 \cdot \mu_{\Delta L^G} + b_3 \cdot \mu_{\Delta L^L} \tag{2.11}$$

Similarly, using equations (A.3), (2.6), (2.7) and (2.8), the variances of the real length deviations in these three cores can be expressed as:

$$(\sigma_{\Delta L_{amp}})^2 = (a_1)^2 \cdot (\sigma_{\Delta L^G})^2 + (b_1)^2 \cdot (\sigma_{\Delta L_{amp}})^2$$

(2.12)

$$(\sigma_{\Delta L_{fil}})^2 = (a_2)^2 \cdot (\sigma_{\Delta L^G})^2 + (b_2)^2 \cdot (\sigma_{\Delta L_{fil}})^2$$

(2.13)

$$(\sigma_{\Delta L_{vic}})^2 = (a_3)^2 \cdot (\sigma_{\Delta L^G})^2 + (b_3)^2 \cdot (\sigma_{\Delta L_{vic}})^2$$

(2.14)

Let the mean values of the global parameter deviation and the local parameter deviations in the parameter-deviation model be zero, i.e.:

$$\mu_{\Delta L^G} = \mu_{\Delta L^L_{amp}} = \mu_{\Delta L^L_{fil}} = \mu_{\Delta L^L_{vic}} = 0$$

(2.15)

According to equations (2.9), (2.10) and (2.11), the required mean values of the channel length deviation defined in equation (2.1) can be satisfied. Let the variances of the global parameter deviation and the local parameter deviations be:

$$(\sigma_{\Delta L^G})^2 = (\sigma_{\Delta L_{amp}^L})^2 = (\sigma_{\Delta L_{fil}^L})^2 = (\sigma_{\Delta L_{vic}^L})^2 = 2.79 \times 10^{-16}$$

(2.16)

In order to satisfy the required variances of the channel length deviation given in equation (2.2), using equations (2.12), (2.13) and (2.14) one can obtain:

$$(a_i)^2 + (b_i)^2 = 1$$

$(i = 1,2,3)$  (2.17)

Additionally, using equation (A.8) and the required correlation coefficients defined in equations (2.3), (2.4) and (2.5), one can obtain:

$$a_1 \cdot a_2 = 0.93 \tag{2.18}$$

$$a_2 \cdot a_3 = 0.93 \tag{2.19}$$

$$a_1 \cdot a_3 = 0.9 \tag{2.20}$$

Using equations (2.17), (2.18), (2.19) and (2.20), the values for  $a_i$  (i = 1,2,3) and  $b_i$  (i = 1,2,3) can be determined as following:

$$a_1 = 0.949$$

,  $b_1 = 0.315$  (2.21)

$$a_2 = 0.980$$

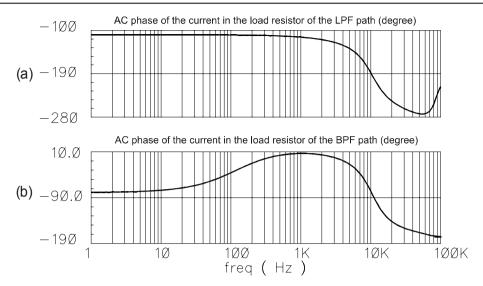

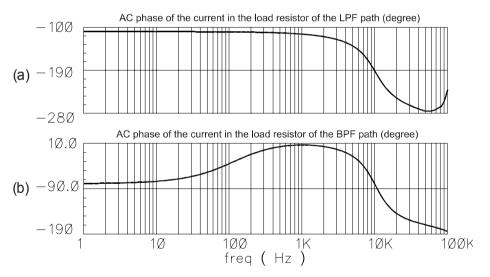

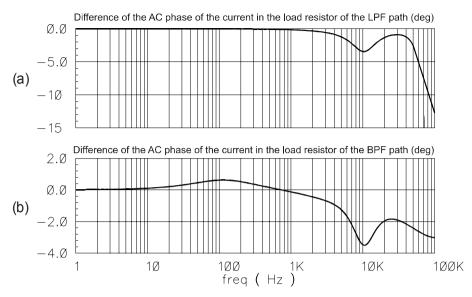

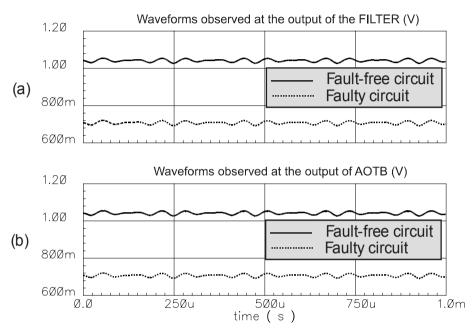

,  $b_2 = 0.199$  (2.22)